PCIe 3.0 delayed until 2011

The next version of the PCI Express bus standard, 3.0, won’t appear until 2010 and not this year as originally anticipated.

Without the publication of the standard we are not going to see any PCIe 3.0-compliant kit until 2011

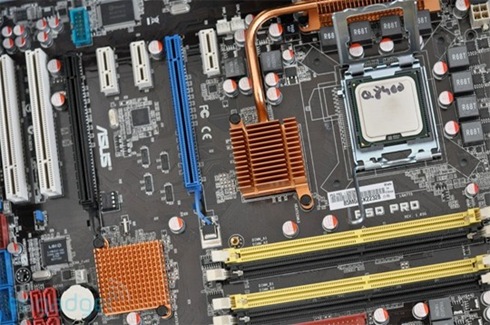

The delay was confirmed by PCI Special Interest Group President Al Yanes. Speaking to PC Magazine, he said the delay was necessary to ensure that the complex new standard retains backwards compatibility with PCIe 1.0 and PCIe 2.0.

PCIe 3.0 ups the bus’ clock to 8GHz. It also ups the previous version’s data-encoding schemes fro 8/10-bit to 128/130-bit. One upshot of changing the encoding scheme is that the cost to data transfer is reduced from 20 per cent to around 1-2 per cent, ensuring more real data is sent at any given clock cycle.

That means PCIe 3.0 will have an effective bandwidth of 7.99Gb/s, compared to the 5Gb/s-rate PCIe 2.0’s effective bandwidth of 4Gb/s. That’s a doubling of bandwidth without the need to aim for 10Gb/s with all the greater signalling issues that 10GHz brings over 8GHz.

Many individuals are less than pleased with this announcement as they believe complete backwards compatibility with products based on the PCIe 1.0 specification are not necessary.

Other individuals have commented on the fact that this delay will make little difference in the grand scheme of things as the current generations technology is nowhere near to saturating the bandwidth of PCIe 2.0